- Základní charakteristiky logického členu

- Logické obvody TTL, CMOS

- Spojování vstupů a výstupů logických členů

- Dynamické vlastnosti logických členů

1. Logické obvody

- TTL - Transistor-Transistor Logic (Tranzistorově-tranzistorová logika)

- CMOS - Complementary Metal-Oxide-Semiconductor (Komplementární kov-oxid-polovodič)

- Logické obvody jsou elektronické obvody, které zpracovávají logické signály. Tyto signály mohou nabývat pouze dvou úrovní (1/0)

- Každá z těchto úrovní odpovídá určitému napětí. Například u TTL logiky (Transistor-Transistor Logic) platí:

- logická 0 → napětí v rozmezí 0 až 0,8 V

- logická 1 → napětí v rozmezí 2 až 5 V

- Logické obvody tvoří základ všech digitálních zařízení – od počítačů, mikroprocesorů, mikrokontrolérů a řídicích jednotek až po měřicí přístroje nebo jednoduché projekty s Arduinem.

2. Základní charakteristiky logického členu

- Každý logický člen (hradlo) je definován parametry, které určují, jak spolehlivě bude v obvodu fungovat:

- Napěťové úrovně:

- : Maximální napětí pro log. 0 a minimální pro log. 1 na vstupu.

- : Napětí, které člen garantuje na výstupu.

- Logický zisk (Fan-out): Udává, kolik vstupů dalších členů stejné řady lze připojit na jeden výstup, aniž by došlo k poruše logických úrovní.

- Statická šumová imunita (Mez šumu): Rozdíl mezi výstupním napětím jednoho členu a vstupním napětím druhého (). Čím je větší, tím je obvod odolnější vůči rušení.

- Proudový odběr: Proud, který člen odebírá ze zdroje v klidu a při spínání.

3. Logické obvody TTL, CMOS

- Založeny na bipolárních tranzistorech. Řídí se proudem do báze. Nulový vstupní odpor.

- Základní stavební prvek je víceemitorový tranzistor, který slouží jako vstupní hradlo.

| Charakteristika | TTL (řada 74) | CMOS (řada 4000 / HC) |

|---|---|---|

| Základní prvek | Bipolární tranzistor | MOSFET tranzistor (P a N) |

| Napájecí napětí () | Pevné: | Široké: až (i více) |

| Logická 0 (vstup) | až | až |

| Logická 1 (vstup) | až | až |

| Logická 0 (výstup) | max. | cca (ideální nula) |

| Logická 1 (výstup) | min. | cca (plné napájecí napětí) |

| Rychlost (Zpoždění ) | Vysoká (stálá, cca ) | Střední/Vysoká (závisí na ) |

| Statická spotřeba | Vysoká (teče stále proud) | Téměř nulová (v klidu nežere) |

| Dynamická spotřeba | Konstantní | Roste s frekvencí (čím víc spíná, tím víc žere) |

| Šumová imunita | Horší (malé rozestupy hladin) | Vynikající (velké rozestupy) |

| Vstupní odpor | Malý (řády ) | Obrovský ( – izolované hradlo) |

-

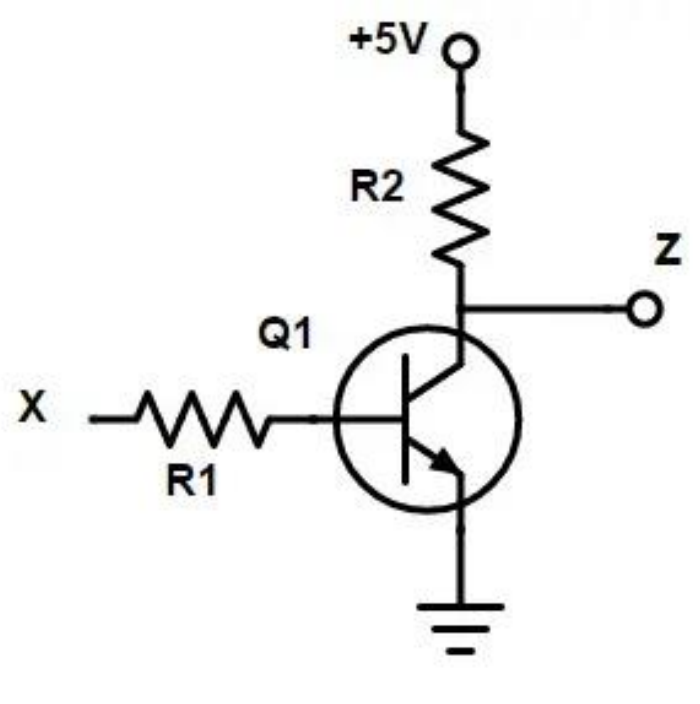

3.1 TTL (NOT)

Schéma TTL invertoru (NOT)

Schéma TTL invertoru (NOT) -

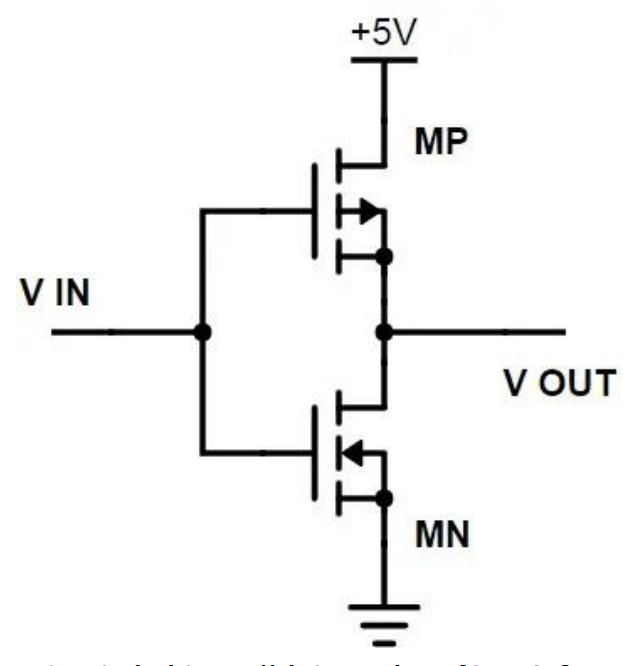

3.2 CMOS (NOT)

Schéma CMOS invertoru (NOT)

Schéma CMOS invertoru (NOT)

4. Spojování vstupů a výstupů logických členů

-

4.1 Spojování vstupů:

- Všechny vstupy, které nejsou používány, musí být připojeny na definovanou logickou úroveň (např. přes odpor na GND nebo Vcc).

- U CMOS hradel je nutné nepoužité vstupy nikdy nenechávat volné, protože mohou zachytit rušení a způsobit nechtěné přepínání.

-

4.2 Spojování výstupů:

- Výstupy nelze spojovat přímo, protože by mohlo dojít ke zkratu mezi různými úrovněmi napětí.

- Výjimkou jsou výstupy s otevřeným kolektorem (open collector) u TTL nebo open drain u CMOS. Ty umožňují spojování výstupů přes společný odpor na napájení.

-

4.3 Připojování mezi TTL a CMOS:

- Pro propojení různých logick se často používají přizpůsobovací obvody - napřiklad odporové děliče nebo tranzistorové převodníky úrovní, aby se zajistila správná interpretace logických úrovní.

5. Dynamické vlastnosti logických členů

- Logický člen nefunguje okamžitě. Tranzistorům chvíli trvá, než se otevřou nebo zavřou.

- Doba zpoždění (): Čas od změny na vstupu po změnu na výstupu.

- : Zpoždění při přechodu z Low do High.

- : Zpoždění při přechodu z High do Low.

- Doba náběhu a doběhu (): Čas, za který se hrana signálu vyškrábe z 10 % na 90 % napětí. Žádný signál není dokonale pravúhlý, vždy je to mírný lichoběžník.

- Maximální kmitočet (): Nejvyšší frekvence, při které obvod ještě stíhá spolehlivě přepínat.